| Author |

Message |

|

BigEd

Joined: Wed Jan 09, 2013 6:54 pm

Posts: 1883

|

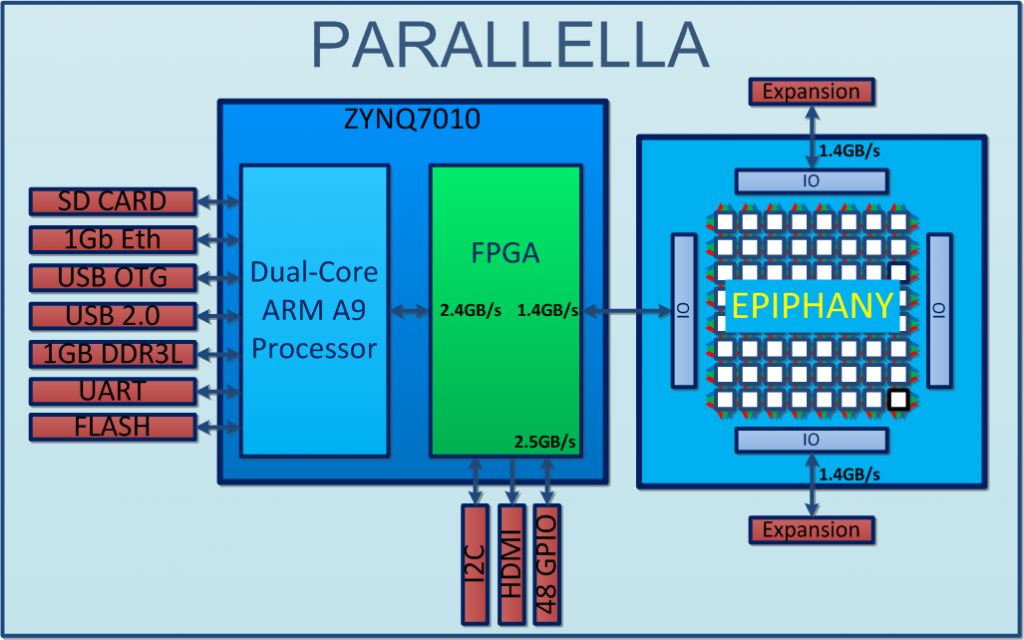

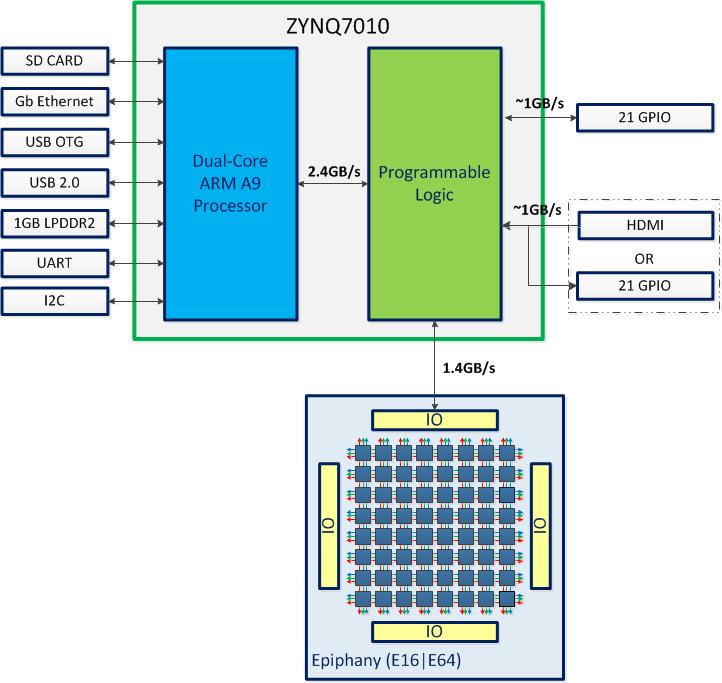

This board is interesting in part because it has an array of parallel CPUs on it, but also it has dual-core ARM and a 32-bit-wide DDR3 RAM, on a chip with FPGA capability (the Zynq7010) - so could be a suitable platform for tinkering with CPU designs.   Presently available to those who sponsored the kickstarter but intended to be $99 retail. Perhaps late this year? Parallella Overview Quote: Zynq-7020 Dual-core ARM A9 CPU

Epiphany Multicore Accelerator (16 or 64 cores)

1GB SDRAM

MicroSD Card

USB 2.0 (two)

Four expansion connectors

Ethernet 10/100/1000

HDMI connection

Ships with Ubuntu OS

Ships with free open source Epiphany development tools that include C compiler, multicore debugger, Eclipse IDE, OpenCL SDK/compiler, and run time libraries.

Dimensions are 3.4” x 2.1” via https://news.ycombinator.com/item?id=5557985

|

| Sun Apr 28, 2013 8:03 pm |

|

|

|

MichaelM

Joined: Wed Apr 24, 2013 9:40 pm

Posts: 213

Location: Huntsville, AL

|

I didn't examine the GitHUB repository extensively, but it appears Parallela's developers have released a set of Verilog FPGA interfaces.

_________________

Michael A.

|

| Mon Apr 29, 2013 10:57 pm |

|

|

|

ElEctric_EyE

Joined: Tue Feb 05, 2013 1:15 pm

Posts: 2

|

I've been looking for prices of the newer Xilinx FPGA SoC offerings, like the Zynq series. Been difficult to find at distributors like Avnet. I assume that Xilinx is still trying to work out the bugs through a very limited release strategy. After all, the Zynq family has been around for at least 6 months now.

|

| Sat May 04, 2013 10:28 pm |

|

|

|

ElEctric_EyE

Joined: Tue Feb 05, 2013 1:15 pm

Posts: 2

|

This is interesting stuff. A simple search led me to the explanation of a 64 core here. They geared it towards C/C++.

|

| Sat May 04, 2013 10:35 pm |

|

|

|

Chuckt

Joined: Wed Jan 16, 2013 2:33 am

Posts: 165

|

I've received a lot of criticism for posting about it on other forums and some of the Xmos users helped me to put it into perspective a little. Quote: "If you think about it for a second, is not that fast. The Core i7-980 @4.5GHz get around 95 GFLOPs compared to Adapteva 16-core at 26 gigaflops. *(even PS3 can do 150GFLOPS, and it has PPC CPU)" The question is whether you can devise algorithms that can make good use of the Epiphany architecture. http://www.xcore.com/forum/viewtopic.php?p=13009#p13009http://www.natami.net/knowledge.php?b=6 ... order=&x=0

|

| Mon May 06, 2013 2:35 am |

|

|

|

BigEd

Joined: Wed Jan 09, 2013 6:54 pm

Posts: 1883

|

Or the question is whether you could put together a Core i7 design nearly as small, cheap or low-power...

It's clear that the major idea here is to get to 64 cores or more. The 16-core device is an early iteration meant to get things going.

Cheers

Ed

|

| Mon May 06, 2013 9:11 am |

|

|

|

BigEd

Joined: Wed Jan 09, 2013 6:54 pm

Posts: 1883

|

I see they have recently taped-out a 1024-core version, called Epiphany-V. 1024 64-bit RISC processors

64-bit memory architecture

64-bit and 32-bit IEEE floating point support

64 MB of distributed on-chip SRAM

1024 programmable I/O signals

Three 136-bit wide 2D mesh NOCs

TSMC 16FF process

4.56 Billion transistors, 117mm^2 silicon area Tape-out means the design is final and is sent to mask-making. Then the masks go to the fab, and eventually chips come out the other end. "Chips will come back from TSMC in 4-5 months." Announcement page: https://www.parallella.org/2016/10/05/e ... processor/HN discussion: https://news.ycombinator.com/item?id=12645661Technical report: http://www.parallella.org/docs/e5_1024core_soc.pdf(Contains lots of info about the implementation, including the amount of effort it took.) Quote: The Epiphany includes is an in-order dual-issue RISC processor with the following key features:

• Compressed 16/32-bit ISA

• IEEE-754 compatible floating-point instruction set (FPU)

• Integer arithmetic logic instruction set (IALU)

• Byte addressable load/store instructions with support for 64-bit single cycle access

• 64-word 6 read/3-write port register file Attachment: Epiphany-V-Implementation.png Attachment: Epiphany-V-Comparison.png

You do not have the required permissions to view the files attached to this post.

|

| Thu Dec 22, 2016 8:56 am |

|

|

|

BigEd

Joined: Wed Jan 09, 2013 6:54 pm

Posts: 1883

|

From the HN discussion: - the $99 board has sold around 10,000 units. Believed to be priced too high to get substantial volume. - this new chip is going to be lower volume and much higher cost. Not for hobbyists - Architecture reference at http://adapteva.com/docs/epiphany_arch_ref.pdf

|

| Thu Dec 22, 2016 9:19 am |

|