National Semiconductor introduced their 32bit CISC family in 1982 - originally called 16000 and later renamed as 32000, with intended family members named according to external bus size. The 32016 had a 16bit wide memory bus.

There's lots of information about the CPU, the history, machines which used it, and a high performance HDL reimplementation for FPGA designs, by Udo Möller:

-

The coprocessor for BBC micro by Acorn -

The Ceres machines by Wirth -

The M32632 HDL core by Udo -

The Titan machines by UdoSee also

Wikipedia of course.

From the

OpenCores page:

Quote:

The M32632 has the following features:

simple instructions are executed in one clock cycle,

8 kByte instruction cache,

8 kByte write-through data cache,

one direct mapped TLB of 256 entries for each cache,

basic floating-point instructions for 32-bit and 64-bit data types,

coprocessor interface for custom instructions,

small size of 15400 LEs,

35 MHz clock speed in Altera Cyclone IV FPGA.

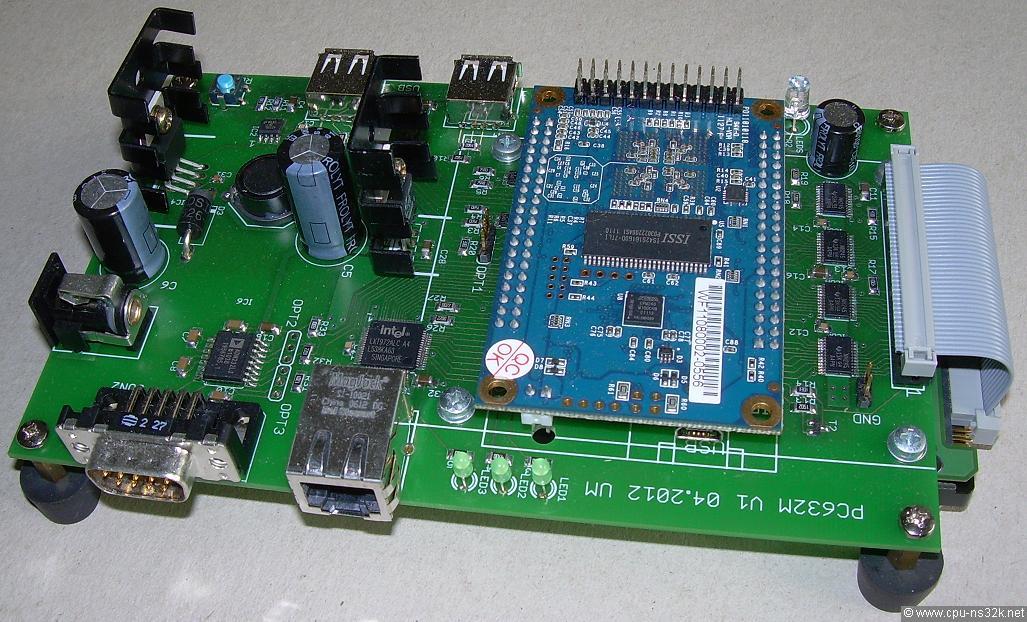

Looks like the M32632 fits on a DE0-Nano board, or presumably on

a cheap lookalike.